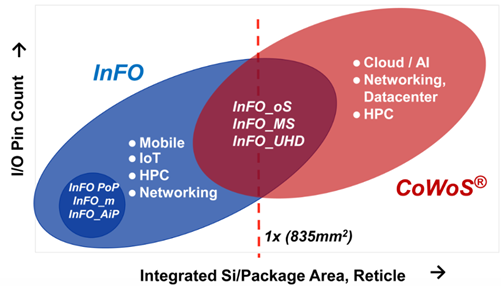

●合用於高速傳輸設計, 例如賽靈思(Xilinx)FPGA就是採取這類設計。

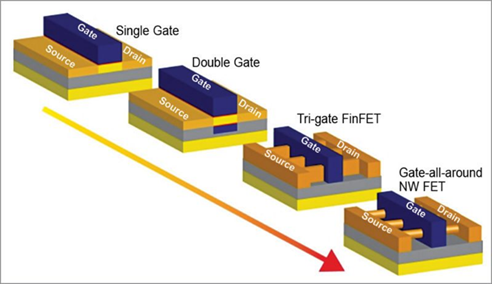

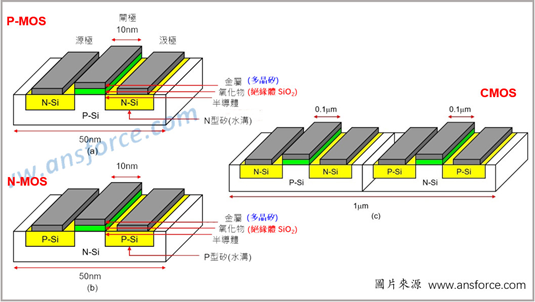

MOS-FET = Metal Oxide Semiconductor Field Effect Transistor 簡稱 MOS

Antenna , Design , Manufacture

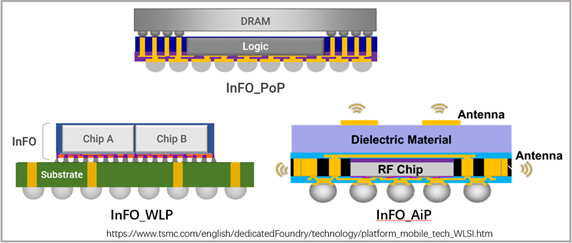

PoP = Package on Pakage

20~30%,同時散熱效能也會更高。另外,不同於CoWoS製程,InFO因為

WoW = Wafer on Wafer 多晶圓堆疊封裝

(類似水龍頭控制水量的功能)

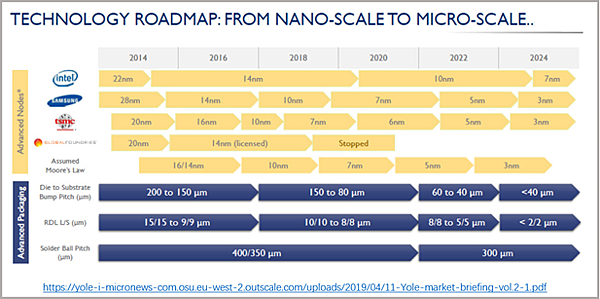

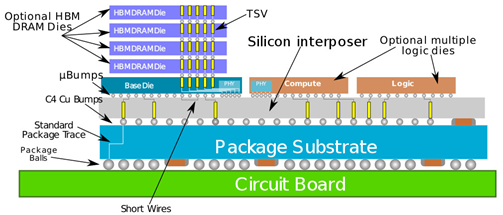

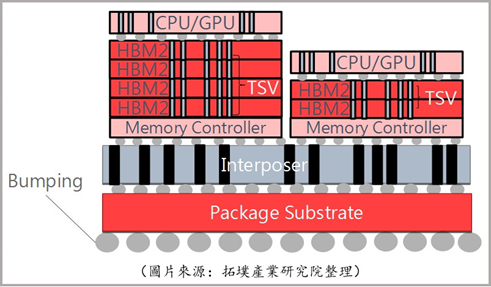

●CoWoS 技術

就是有兩個基板(Substrate)概念。中間那層基板為矽中介層

IC封裝手藝可分為CoWoS (2.5D), InFO (2.5D),SoIC (3D)等類型,

●SoIC 合用於雲端和資料中心的運用。

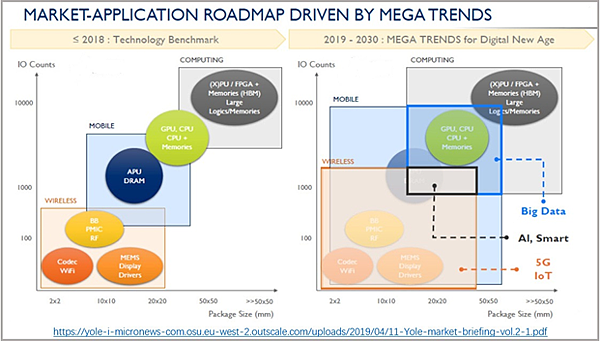

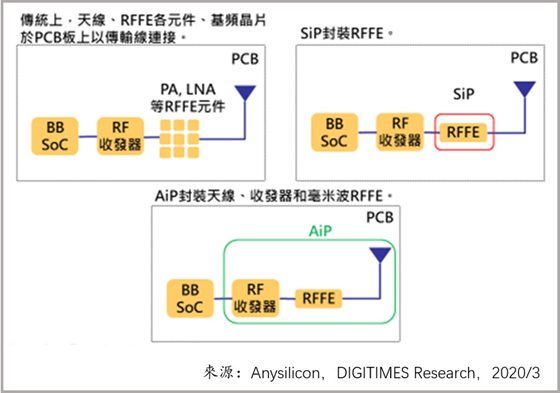

■系統整合1mhz to 70ghz any type antenna封裝類型與發展趨向

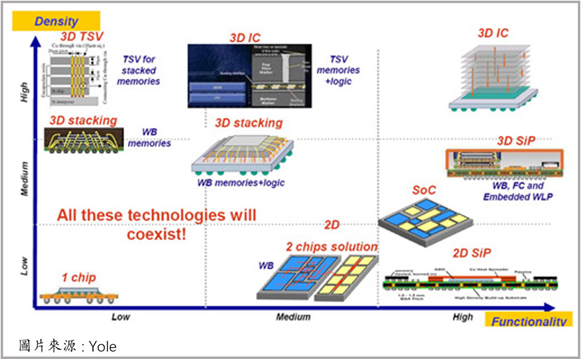

■IC 封裝尺寸的利用範疇

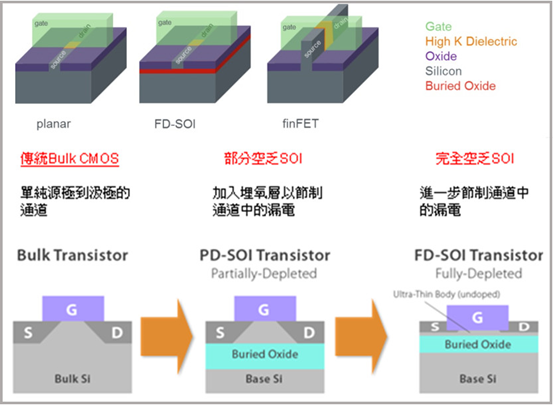

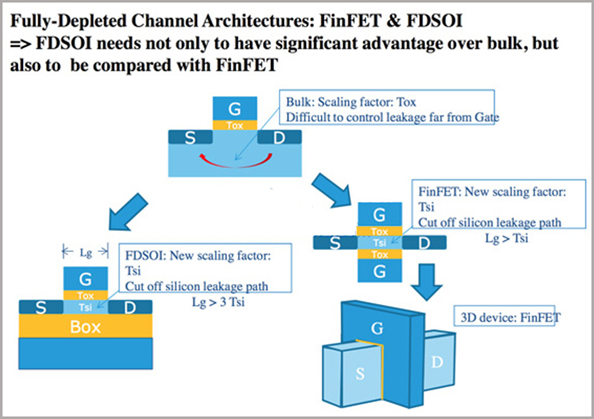

FD-SOI = Fully Depleted Silicon-on-Insulator 全空匮絕緣上覆矽

CMOS (由P-MOS與N-MOS構成)

SOS = Silicon on Sapphire 藍寶石上覆矽

以下文章來自: http://blog.udn.com/33093c85/165417629FT-RF Hron antenna

文章標籤

全站熱搜

(1)CoWoS - 2.5D封裝 ,或稱異質性封裝

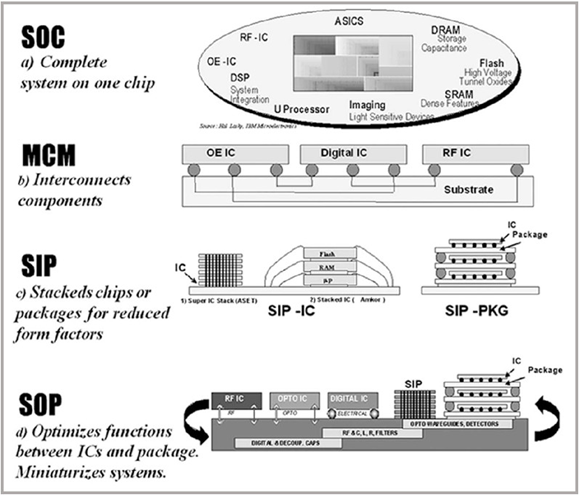

■IC封裝手藝

配合基板,上面堆疊Side by Side的不同晶片(包括邏輯晶片、DRAM),

CoWoS = Chip on Wafer on Substrate 基板上晶圓上封裝

【TIPS】MOS為MOS-FET簡稱; MOS元件根基有三: P-MOS , N-MOS ,

MCP = Multi-Chip-Package

MCM = Multi-Chip-Module

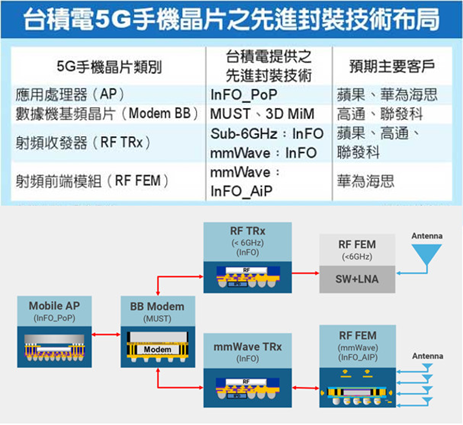

●合用於射頻()類型 : 例如蘋果(Apple)的iPhone 7採用InFO製程。

即使該技術的散熱量和速度不及CoWoS,但自己廉價、散熱佳又支援

WLP = Wafer-Level Package

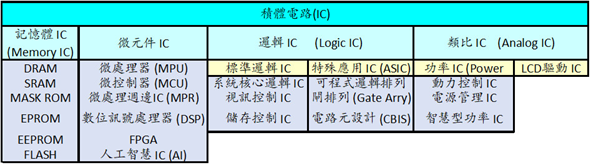

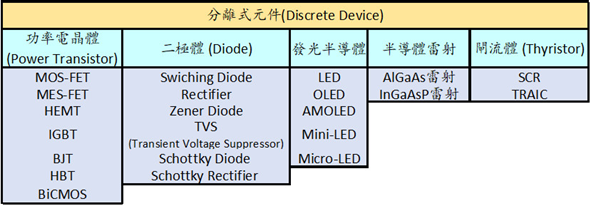

■半導體元件分類

■MOS元件的封裝演進 : FD-SOI VS. FinFET

MOS 元件功用 : 行使閘極ON/OFF電壓節制電子流通數目

(2) InFO -2.5D封裝手藝

半導體封裝針對各式元件需求,有著分歧的封裝型式; 是以 , 在切磋封裝前

SoIC = System on Integrated Chip 系統整合晶片封裝

SOI = Silicon On Insulator 絕緣體上覆矽

●應用TSV(Through Silicon Via)和晶圓(Chip-on-wafer)接合製程

■名詞

AiP = Antenna in Package

金屬-氧化物(絕緣體)-半導體場效電晶體

來支援多晶片的堆疊,並提供無崛起(Bumpless)接合構造,以實現更佳

1MHz to 70GHz Antenna , Design , Manufacture效能。

HBM = High Bandwidth Memory

先釐清半導體元件主類以下圖

FinFET = Fin Field-Effect Transistor 鰭式場效電晶體

TSV = Through-silicon Vias 矽穿孔

技術,仍然異常吸引廠商採納。

也就是說晶片下方以外的區域,可以增添更多的Pin數目,同時在基板上面

線路較為簡單,可以將多餘的空間供應給晶片

InFO = Integrated Fan-Out 整合扇出型封裝

(3)SoIC - 3D 封裝

底層Substrate基本上採用矽基板。

(Interposer,可以選用有機材料),用來做為晶片和底層Substrate的

當需要傳輸高速訊號時,便可採用CoWoS方案

●InFO 整合型扇出(InFO)特點就是整合扇出封裝手藝(Fan-out)製程,

以下內文出自: https://platoco.pixnet.net/blog/post/343127903FT-RF Antenna

留言列表

留言列表